Ampere<sup>®</sup> Altra<sup>®</sup> Family 64-Bit Multi-Core Processor SoC Baseboard Management Controller Interface Specification February 9, 2023 Document Issue 1.42

## Contents

| 1. | Ove  | erview                                  | 5  |

|----|------|-----------------------------------------|----|

| 2. | Har  | dware Interfaces                        | 6  |

|    | 2.1  | Processor-to-BMC Hardware Connectivity  | 6  |

|    | 2.2  | GPIO Table                              | 7  |

|    | 2.3  | Other Design Considerations             | 8  |

| 3. | Pro  | cessor to BMC Communication             | 11 |

|    | 3.1  | System Management Bus (SMBus)           | 11 |

|    | 3.2  | Out-of-Band Communication               | 11 |

|    | 3.3  | In-Band Communication                   | 12 |

| 4. | Det  | ailed Software Functions                | 12 |

|    | 4.1  | Host-to-BMC Communication               | 12 |

|    | 4.2  | BMC-to-Processor Communication          | 13 |

|    | 4.3  | Error Detecting and Reporting           | 13 |

|    | 4.4  | Fail-Safe Feature                       | 13 |

| 5. | Pro  | cessor Data Information Specification   | 15 |

|    | 5.1  | Extended LM75 Format                    | 15 |

|    | 5.2  | Identification Definitions              | 15 |

|    | 5.3  | Capability Register Definitions         | 16 |

|    | 5.4  | Logical Power Sensor Definitions        | 17 |

|    | 5.5  | GPI Mask Register Definitions           | 21 |

|    | 5.6  | GPI Source Registers                    | 22 |

|    | 5.7  | GPI Status Registers                    | 25 |

|    | 5.8  | Core Error Register Definitions         | 28 |

|    | 5.8. | 1 CE/UE Error Data Record Format        | 29 |

|    | 5.9  | Memory Error Register Definitions       | 31 |

|    | 5.10 | RAS Internal Error Register Definitions | 32 |

|    | 5.11 | Boot Stage Register Definitions         | 34 |

|    | 5.12 | NVDIMM-N Status Register Definitions    | 38 |

|    | 5.13 | PCIe Error Register Definitions         | 41 |

|    | 5.14 | Other Errors                            | 42 |

|    | 5.15 | ACPI State Register Definitions         | 43 |

| 6. | Pro  | cessor Boot Progress Codes              | 45 |

| 7. | Doc  | cument Revision History                 | 48 |

# Figures

| Figure 1: Processor-to-BMC Hardware Connectivity | 10 |

|--------------------------------------------------|----|

| Figure 2: Fail-Safe Operation Sequence           | 14 |

# Tables

| Table 1: GPIO Assignments                                           | 7  |

|---------------------------------------------------------------------|----|

| Table 2: Alert and Additional Miscellaneous Signals                 | 9  |

| Table 3: Processor Register Identification Definitions              | 15 |

| Table 4: Capability Register Definitions                            | 16 |

| Table 5: Logical Power Sensor Register Definitions                  |    |

| Table 6: GPI Mask Register Definitions                              | 21 |

| Table 7: GPI Source Register Definitions                            | 23 |

| Table 8: GPI Interrupt Alert Behaviors Definitions                  | 24 |

| Table 9: GPI Status Register Definitions                            | 25 |

| Table 10: Core Register Definitions                                 |    |

| Table 11: CE/UE Error Type                                          | 29 |

| Table 12: Hardware Error Type 0x00 to 0x0B CE/UE Data Record Format | 29 |

| Table 13: Hardware Error Type Details                               | 30 |

| Table 14: Memory Error Registers                                    | 31 |

| Table 15: RAS Internal Error Registers                              | 32 |

| Table 16: Boot Stage Registers                                      | 34 |

| Table 17: NVDIMM-N Status Registers                                 |    |

| Table 18: PCIe Error Registers                                      | 41 |

| Table 19: Other Error Registers                                     |    |

| Table 20: ACPI State Registers                                      | 43 |

| Table 21: Processor Boot Progress Codes                             | 45 |

## 1. Overview

This specification describes the high-level interface for supporting a Baseboard Management Controller (BMC) and focuses on high-level hardware and software requirements to support a BMC on a platform containing Ampere Computing<sup>®</sup> Altra<sup>®</sup> or Altra<sup>®</sup> Max processors, also call Systems-on-Chip (SoCs).

Note: In this specification, the term "processor" refers to both Altra and Altra Max processors.

BMC designs generally result from system-level architectural requirements. In this document, statements are sometimes made about what an implementation "should" do. Such statements are intended as guidelines, consistent with common practice, and do not represent requirements of the processor.

Note: This specification is subject to change.

## 2. Hardware Interfaces

### 2.1 Processor to BMC Hardware Connectivity

The generic hardware connectivity requirements between one or two processors, including processors in dual-socket (2P) systems, and the BMC include:

- An SMBus-based I2C\_4 bus must be configured as a master and attached to an Inter-Integrated Circuit (I<sup>2</sup>C) slave port of the BMC. This link between the processor and the BMC is for host-initiated requests. The I2C\_4 bus is the SMBus System Interface (SSIF) between the processor and the BMC. The processor I2C\_4 ALERT\_L<sup>1</sup> input should connect to the BMC output (I2C4\_ALERT\_L), which functions as the BMC\_ALERT\_L signal from the BMC. The BMC uses this signal to alert the processor when the BMC sends a message to the host over SSIF. In 2P systems, only the master socket I2C\_4 bus and I2C\_4 ALERT\_L signals connect to the BMC.

- A SMBus-based I2C\_3 bus must connect the processor to another I<sup>2</sup>C bus of the BMC. The processor I2C\_3 port is configured as an I<sup>2</sup>C slave and the BMC I<sup>2</sup>C port is configured as a master. This is a point-to-point link between the BMC and the processor for BMC-initiated requests. In 2P systems, the I2C\_3 signal of each socket connects to the same BMC I2C bus. The processor I2C\_3 SMBALERT (ALERT\_L) output is used as the SMB\_ALERT\_L signal to alert the BMC of critical events or errors. In 2P systems, the I2C\_3 alert signal for each socket connects to the BMC. The decision to OR-tie the signals is up to the system implementer.

- The processor UARTO should pipe processor console output to the BMC to support Serial Over LAN (SOL) functionality with a remote station.

- A processor General-Purpose Input/Output (GPIO) output (CPU\_FW\_BOOT\_OK), acting as a Software Ready signal, should connect to an input GPIO of the BMC. This informs the BMC that the processor is ready to communicate with the BMC. In a 2P system, both socket output signals connect to the BMC.

Note: It is not recommended to OR-tie these signals.

- The non-secure (NS) GPIO23 input signal should connect to an output GPIO (BMC\_CPU\_SHD\_REQ\_L) of the BMC, which functions as a graceful shutdown request signal from the BMC. Upon receiving this signal, the processor performs a graceful shutdown. This signal is needed for the Master socket only in 2P systems.

- A processor GPIO9 output (CPU\_BMC\_SHD\_ACK\_L) connects to a GPIO interrupt input of the BMC. This informs the BMC that the processor completed a graceful shutdown, previously triggered either by the BMC using the NS GPIO23 input, or by software. The BMC in turn should turn off the PSU upon receipt of this signal. This signal is needed for Master socket only when 2P is deployed.

- A processor GPIO10 output (CPU\_REBOOT\_ACK\_L) connects to a GPIO interrupt input of the BMC to inform the BMC that a processor reboot executed from the Operating System (OS). This signal is required for the master socket only in 2P systems.

- The processor SYS\_RESET\_L signal should connect to the BMC so that the BMC can reset the processor. In a 2P system, both socket signals connect to the BMC.

Note: It is not recommended to OR-tie these signals.

- The CPU\_BMC\_OVERTEMP\_L (also known as External OVERTEMP) output signal from the processor must connect to the BMC to alert the BMC of critical temperature conditions requiring power shutdown. In 2P systems, both socket output signals connect to the BMC. The decision to OR-tie the signals is up to the system implementer.

- The CPU\_BMC\_HIGHTEMP\_L signal of the processor (also known as *External HIGHTEMP*) is bidirectional and by default is an input. The CPU drives this signal as an output only when firmware detects a high temperature condition. The BMC uses this signal, which must connect to the BMC GPIO output, to notify the processor of HIGHTEMP conditions observed by the BMC. The SoC VRD and Cluster Processor Module (CPM) VRD VRHOT\_L signals also drive the CPU\_BMC\_HIGHTEMP\_L signal. When the processor detects external HIGHTEMP signals, the processor reduces CPU frequencies until the signals clear. In 2P systems, both socket signals connect to the BMC.

**Note**: It is not recommended to OR-tie these signals.

<sup>&</sup>lt;sup>1</sup> The ALERT\_L mnemonic is used generically to denote the I2C SMBALERT# input or output pins. Document Issue 1.42 Ampere Computing Proprietary and Confidential

- A CPU\_FAULT\_ALERT signal from the processor should connect to a BMC GPIO interrupt input to inform the BMC that the processor encountered a fault or unrecoverable error while booting before SCP\_BOOT\_OK is asserted. In 2P systems, a CPU\_FAULT\_ALERT signal is required per socket.

- A PMIN (GPIO12) signal connects to a BMC output that functions as the power management minimum power control request signal. Upon receiving a BMC request, the processor immediately throttles to the lowest frequency/voltage. In 2P systems, a PMIN signal is required per socket.

## 2.2 GPIO Table

*Table 1* provides more detailed descriptions of the signals described in the preceding section.

#### Table 1: GPIO Assignments

| MNEMONICS          | SIGNAL    | DIR FROM<br>PROCESSOR | SOCKETO | SOCKET1 | COMMENTS                                                                                                                                                                                       |

|--------------------|-----------|-----------------------|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU_FW_BOOT_OK     | GPIO8     | OUT                   | Yes     | Yes     | Set by the host to inform the BMC if<br>the host is in ready status; HIGH if<br>the host is in ready status.                                                                                   |

| BMC_CPU_SHD_REQ_L  | GPIO23    | IN                    | Yes     | N/A     | Input to the host from the BMC to request a graceful shutdown; LOW level triggered.                                                                                                            |

| CPU_SHD_ACK_L      | GPIO9     | OUT                   | Yes     | N/A     | Output from the host to BMC.<br>Asserted LOW to acknowledge a<br>shutdown request from the BMC.<br>The processor also asserts this<br>when it finishes a soft shutdown<br>request from the OS. |

| CPU_REBOOT_ACK_L   | GPIO10    | OUT                   | Yes     | N/A     | Output from the host to the BMC.<br>Asserted LOW to notify the BMC<br>that a software reset executed from<br>the OS.                                                                           |

| CPU_BMC_OVERTEMP_L | OVERTEMP  | OUT                   | Yes     | Yes     | Output LOW from the host to the<br>BMC to indicate an OVERTEMP<br>event. The OVERTEMP event<br>initiates a power-off sequence for<br>the entire processor.                                     |

| BMC_CPU_RST_L      | SYS_RESET | IN                    | Yes     | Yes     | Input to the host from the BMC or<br>Reset button. Asserted LOW to<br>reset the host.                                                                                                          |

| I2C4_ALERT_L       | ALERT     | IN                    | Yes     | N/A     | LOW level triggered from BMC to<br>host to notify the host of an event<br>on the SSIF interface.                                                                                               |

| CPU_BMC_HIGHTEMP_L | HIGHTEMP  | Bi-directional        | Yes     | Yes     | At boot, this is configured as in<br>input. At internal high temperature,<br>this is configured as an output to<br>BMC. On BMC detection of high<br>temperature, assert by BMC.                |

| MNEMONICS       | SIGNAL | DIR FROM<br>PROCESSOR | SOCKETO | SOCKET1 | COMMENTS                                                                                                   |

|-----------------|--------|-----------------------|---------|---------|------------------------------------------------------------------------------------------------------------|

| I2C3_ALERT_L    | ALERT  | OUT                   | Yes     | Yes     | Output from the host to BMC to notify the BMC of an event/error on the I <sup>2</sup> C slave bus.         |

| PMIN            | GPIO12 | IN                    | Yes     | Yes     | The BMC drives the signal HIGH to<br>trigger host throttle to the lowest<br>frequency/voltage              |

| CPU_FAULT_ALERT | S-GPIO | OUT                   | Yes     | Yes     | High level triggered from the host<br>to notify the BMC that the CPU has<br>a fault/non-recoverable error. |

### 2.3 Other Design Considerations

- The boot EEPROM must connect to an I<sup>2</sup>C bus configured as master on the processor side, preferably on its own bus. In 2P systems, both I<sup>2</sup>C buses connect to the same boot EEPROM. Software ensures access control.

- The BMC may have board-specific requirements to access the boot EEPROM for firmware upgrades. If so, additional circuitry may be needed to enable the boot EEPROM to connect to a BMC master I<sup>2</sup>C interface. This can be done using an I<sup>2</sup>C mux or I<sup>2</sup>C bus isolators. The processor I2C1 supports multi-master operations, so there is no need for an I2C mux between the I<sup>2</sup>C buses of the two sockets to access the boot EEPROM.

- The BMC must connect directly to the I2C\_X bus and not through any I<sup>2</sup>C mux or expander.

- Slave devices accessible to and controlled directly by the BMC connect to a BMC I<sup>2</sup>C bus configured as master. Such devices include the fan controller, Field Replaceable Unit (FRU) EEPROM, ambient temperature sensor, and additional on-board thermal and power sensors.

- Slave devices accessible to and controlled directly by the processor connect to a processor master I<sup>2</sup>C bus. These devices include, but are not limited to, the Enhanced Small Form-Factor Pluggable (SFP+) modules, Real-Time Clock (RTC), GPIO expander, and so on.

- The RTC, if present, must connect to a processor master I2C\_6 bus.

- The LED controller, if present, must connect to a processor master I<sup>2</sup>C bus under the control of the System Control Processor (SCP).

- The EVENT output signal from SPD DDR EEPROM connects to an ALERT\_L input of the processor to notify the processor of any critical DDR temperature events.

- The ALERT output signals from the SoC VRD, CPM VRD, and DDR VRD(s) should connect to the PMALERT input signal to alert the processor of critical power conditions.

- The VRHOT output signals from the DDR VRD(s) also connect to the PMALERT signal.

- A BMC\_OK signal from the BMC connects to an input GPIO of the processor. The BMC triggers this to notify the processor that the BMC is ready to receive messages and requests on SSIF.

- A CPU\_SLAVE\_PRESENT\_L signal from hardware circuitry connects to the BMC and processor Master Socket GPIO inputs. This signal indicates that a Host Slave Socket is present.

- SCP\_AUTH\_FAILURE (GPI015) is an output signal from both sockets in a 2P system to the BMC. The signal notifies the BMC when a SCP firmware authentication fails (SMpro or PMpro images). The BMC, upon receipt of this notification, may switch to a failover EEPROM and reset the system. Note that ROM boot failures of the SCP only have the fault LED asserted (or blink) in a specific pattern.

- HOST\_AUTH\_FAILURE\_L (GPIO7) is an output signal from master sockets in a 2P system to the BMC. The signal notifies the BMC when ATF BL1, BL2, BL31, BL32, UEFI BL33 authentication fails or when host failsafe procedure fails.

**Note:** HOST\_AUTH\_FAILURE\_L (GPIO7) is also asserted when BL33 certification is not included in the SPI-NOR image even when BL33 authentication is not enabled. To avoid this condition, ensure that a BL33 certification is included. In such cases, only an existing certification is needed to avoid this.

Table 2 summarizes the alert signals and additional signals not listed in Table 1.

### Table 2: Alert and Additional Miscellaneous Signals

| MNEMONIC            | SIGNAL  | DIR FROM<br>PROCESSOR | SOCKETO | SOCKET1 | COMMENTS                                                                                                                                                                                                                                     |

|---------------------|---------|-----------------------|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMALERT             | PMALERT | IN                    | Yes     | Yes     | LOW level triggered to notify the host<br>about events from I <sup>2</sup> C device(s)<br>connected to the I2C1 bus, such as<br>DIMM high temperature.                                                                                       |

| ALERTX_N            | ALERT   | IN                    | Yes     | Yes     | Alert signal input from DIMM EVENT<br>pin(s) that indicate that the DIMM<br>temperature exceeds the warning<br>threshold.                                                                                                                    |

| BMC_OK              | GPI 0   | IN                    | Yes     | N/A     | The BMC triggers HIGH level to notify the processor that the BMC is ready to receive SSIF messages.                                                                                                                                          |

| MASTER_2P           | GPIO    | IN                    | Yes     | Yes     | On the master, the signal is asserted. On<br>the slave, it is deasserted.<br><b>Note</b> : The master socket must also be<br>routed to the BMC.                                                                                              |

| SLAVE_PRESENT_L     | GPIO    | IN                    | Yes     | No      | -                                                                                                                                                                                                                                            |

| SLAVE_PRESENT_L     | GPIO    | OUT                   | No      | Yes     | The signal must be routed to the BMC to indicate the presence of the slave socket to the BMC.                                                                                                                                                |

| SCP_AUTH_FAILURE    | GPI15   | OUT                   | Yes     | Yes     | SCP firmware authentication failure.                                                                                                                                                                                                         |

| HOST_AUTH_FAILURE_L | GPI7    | OUT                   | Yes     | No      | LOW level triggered to notify the host<br>about BL1, BL2, BL31, BL32, BL33<br>authentication failure, or failsafe<br>procedure failure.<br><b>Note:</b> HOST_AUTH_FAILURE_L (GPIO7) is<br>also asserted when BL33 certification is           |

|                     |         |                       |         |         | not included in the SPI-NOR image even<br>when BL33 authentication is not<br>enabled. To avoid this condition, ensure<br>that a BL33 certification is included. In<br>such cases, only an existing certification<br>is needed to avoid this. |

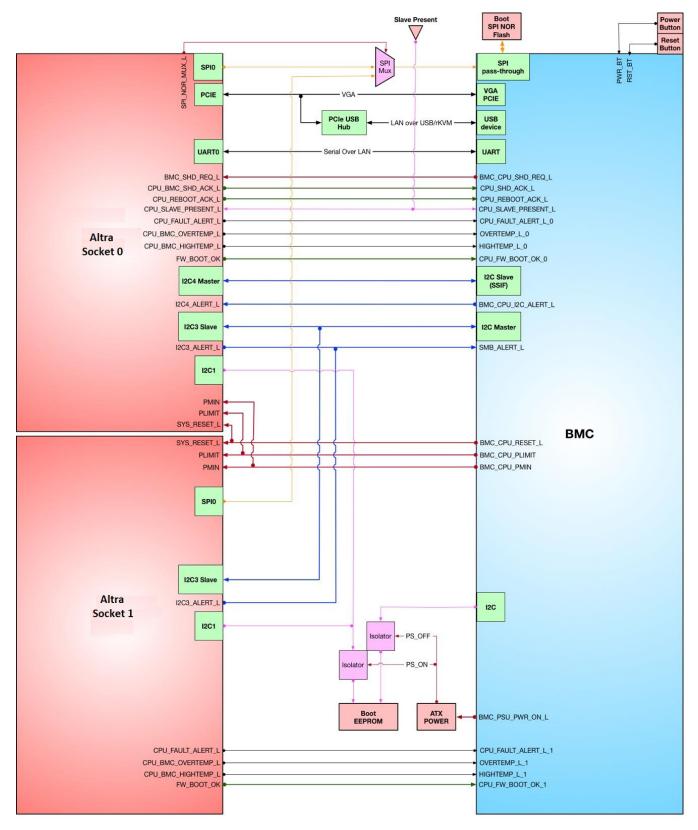

Figure 1 illustrates an example of the processor to BMC hardware connectivity.

#### Figure 1: Processor-to-BMC Hardware Connectivity

## 3. Processor to BMC Communication

### 3.1 System Management Bus (SMBus)

The SMBus is a two-wire interface that various system components use to communicate with each other.

As described previously, the processor must connect to the BMC using the processor I<sup>2</sup>C slave interface on the SMBus. The BMC must always be an I<sup>2</sup>C master and the S-GPIO must always be an I<sup>2</sup>C slave on the SMBus. To the BMC, the processor appears as an I<sup>2</sup>C slave device used to query thermal sensors and VRD telemetry data such as VRD output power, VRD temperature, or sensors/system event configuration supported by the processor software. Because the BMC is the I<sup>2</sup>C master and the processor is the slave, the BMC always issues I<sup>2</sup>C master read requests and the processor responds to those requests in the same read transaction.

The processor must connect to another  $I^2C$  interface of the BMC using another  $I^2C$  bus. On this bus, the processor is the  $I^2C$  master, and the BMC is the  $I^2C$  slave. To the processor, the BMC appears as an  $I^2C$  slave device on this  $I^2C$  bus. This connectivity is used for host-initiated communications with the BMC.

• The SMBus standard specifies an optional signal, SMBALERT, which provides an interrupt line for devices that want to

trade their ability to master for a pin. SMBALERT is an active-low wired-OR signal like the SMBCLK and the

SMBDAT signals. SMBALERT is used with the SMBus General Call Address. When the processor needs to

communicate with the BMC, the processor asserts the SMBALERT interrupt to the BMC.

• When one BMC controls both processors in a 2P system, each processor has only one interrupt and the multiple interrupt lines are wire-ORed to the BMC for SMBALERT. The BMC processes the interrupt and simultaneously

accesses all SMBALERT devices using the Alert Response Address (ARA). Only devices that pull SMBALERT low

acknowledge the ARA. In the one-device-per-interrupt case, the same processor always acknowledges the ARA.

• In a 2P configuration, the I2C\_3 bus of each processor must connect to the BMC. Each processor independently provides sensor information to the BMC. While the master I2C\_4 connects only to the BMC, the host-initiated request is driven by UEFI and the OS. At that stage of the boot process, the system is considered a uniform system and a single connection is enough.

### 3.2 Out-of-Band Communication

The processor does not support Out-of-Band (OOB) communication; out-of-band communication exists only for the BMC. As a reference, ARM specifies that OOB communication must use Redfish API. A remote management station connects to the BMC using the BMC OOB interfaces, such as the LAN port, and issues Redfish API to the BMC. On the processor platform, physical on-board BMC access is through the BMC management Ethernet. For example, the network manager could run remote management software or Redfish API tools on a workstation and send a Redfish API to a specific BMC. The remote software opens a network connection directly to the BMC and works on the standard Redfish API for the given commands.

### 3.3 In-Band Communication

As required by the Server Base Management Guide (SBMG) specification for level M2, these interfaces are required:

- Redfish

- Intelligent Platform Management Interface (IPMI)

For Redfish support, the physical interface between the host and the BMC is an Ethernet type interface. On the processor platform, this is achieved using PCIe USB Ethernet. The processor supports the Redfish protocol (0x4h) with SMBIOS Type 42. Refer to *Redfish Host Interface Specification* at

https://www.dmtf.org/sites/default/files/standards/documents/DSP0270\_1.0.0.pdf for details.

For IPMI, in-band communication is achieved using SSIF over  $I^2C$  or SMBus. IPMI defines standard system interfaces that system software can use to pass IPMI messages to the BMC. These interfaces are Keyboard Controller Style (KCS), System Management Interface Chip (SMIC), Block Transfer (BT), and SSIF. Over  $I^2C$  or SMBus, the processor supports only SSIF. Applications must communicate with the BMC using the /dev/ipmi0 SSIF interface provided by the processor Linux kernel.

Detailed information about in-band communication is beyond the scope of this document.

### 3.4 Host-to-BMC Communication

Communication between host applications and the BMC uses IPMI over the SSIF /dev/ipmi0 interface using the BMC slave address.

# 4. Detailed Software Functions

### 4.1 BMC-to-Processor Communication

Communication between BMC and the processor uses the processor Register Map. To query sensor data and status, the BMC can read the processor Register Map using the BMC I<sup>2</sup>C master interface connected to the processor I<sup>2</sup>C slave.

### 4.2 Error Detecting and Reporting

The processor triggers SMBALERT to notify the BMC of critical or catastrophic errors. These errors and events trigger an alert to the BMC:

- System events such as platform booting/reset and so on.

- Thermal and power events

- Core errors

- Memory errors

- PCle errors

- Other errors

- Advanced Configuration and Power Interface (ACPI) state changes

Upon receiving the alert, the BMC must access the Register Map General-Purpose Interrupt (GPI) to identify the error source and then read the associated status information to determine the error details.

### 4.3 Fail-Safe Feature

During the boot process, the system may not boot correctly when there are hardware issues, such as:

- Incorrect voltage for core/SoC/DRAM (changed manually).

- Incorrect DRAM parameters (speed/interleaving mode, and so on) resulting in incorrect configuration.

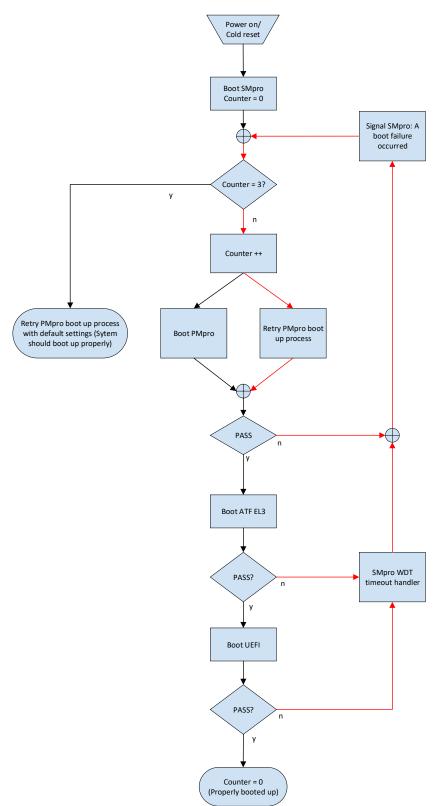

These affect the processor boot process without any scope for recovery. To mitigate such situations, software implements a fail-safe<sup>2</sup> feature in which the system boots itself with default settings after a certain number of boot failures.

The fail-safe feature is implemented on SMpro, which always boots. SMpro maintains a counter that is initialized to 0 upon either power-on or cold reset. After SMpro boots properly and is ready to boot PMpro, the counter is set to 1. If the system boots in a clean manner to a stage which is considered good (and which is defined at the end of the UEFI BIOS stage in the boot process), the counter is cleared, indicating that the system booted successfully. If the boot failure reaches its maximum set limit, SMpro restarts the boot process in fail-safe mode. This fail-safe boot mode state is propagated to the software components in the boot process: PMpro, ATF, and UEFI.

The boot failure limit is stored in non-volatile storage. By default, the retry count is 3.

Document Issue 1.42

<sup>&</sup>lt;sup>2</sup> Fail-safe is a BMC feature for Altra family processors.

*Figure 2* illustrates the fail-safe operation sequence.

#### Figure 2: Fail-Safe Operation Sequence

The BMC software is expected to handle and log such information.

## 5. Processor Data Information Specification

The processor provides various information to the BMC through the I<sup>2</sup>C register map interface described in this section.

### 5.1 Extended LM75 Format

The command/address (offset) format and access mechanism from the BMC to I<sup>2</sup>C registers as provided by the processor register map is based on the National Semiconductor LM75 format.

However, the LM75 format imposes two limitations:

- The specification of the Pointer Register (to select which registers to read/write) provides only two bits for register selection, limiting the number of accessible registers to four.

- The returned value for a temperature is only one byte, enabling temperatures to be reported only in the range of 0–125°C.

To accommodate a wider range of logical functions and customer requirements, the processor  $I^2C$  register map is extended to remove these restrictions:

- The Pointer Register can use up to eight bits, supporting the selection of up to 256 registers.

- Data values use two bytes instead of only one.

Note: In some cases, data values may go up to 48 bytes.

These are the register access types:

- R Read only

- W Write only

- R/WRead and write

- W1C Write 1 to clear

### 5.2 Identification Definitions

Table 3 summarizes the processor register identification definitions.

#### Table 3: Processor Register Identification Definitions

| REGISTER<br>ADDRESS | REGISTER NAME                     | INITIAL<br>VALUE | ACCESS<br>TYPE | BYTE | REGISTER DESCRIPTION                                                                                                                                  |

|---------------------|-----------------------------------|------------------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0                 | Register Specification<br>Version | 0x5              | R              | 0    | Major version of this specification (in hexadecimal).<br>For example, if the major version of this<br>specification is 5.0, this value is 0x05.       |

|                     |                                   | 0x1              | R              | 1    | Minor version of this specification (in hexadecimal).<br>For example, if the minor version of this<br>specification is 4510, then this value is 0x0A. |

| 0x1                 | SCP Version                       | -                | R              | 0    | Major Firmware version (in hexadecimal) of the SCP firmware.                                                                                          |

|                     |                                   | -                | R              | 1    | Minor Firmware version (in hexadecimal) of the SCP firmware.                                                                                          |

| 0x9                 | SCP Build ID (lower)              | _                | R              | 0    | Build firmware build ID.<br>Byte 0 of firmware build ID:<br><b>Note:</b> The offset is non-sequential.                                                |

|                     |                                   | _                | R              | 1    | Byte 1 of firmware build ID.                                                                                                                          |

| REGISTER<br>ADDRESS | REGISTER NAME        | INITIAL<br>VALUE | ACCESS<br>TYPE | BYTE | REGISTER DESCRIPTION                                                                                                                      |

|---------------------|----------------------|------------------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0xA                 | SCP Build ID (upper) | I                | R              | 0    | Byte 2 of the firmware build ID.                                                                                                          |

|                     |                      | 0x00             | R              | 1    | Byte 3 of the firmware build ID.                                                                                                          |

| 0x2                 | Manufacturer ID      | 0x3A             | R              | 0    | Manufacturer ID, LSB first, binary encoded.                                                                                               |

|                     |                      |                  |                |      | This is the Internet Assigned Numbers Authority<br>(IANA) Private Enterprise ID following the IPMI<br>specification for Manufacturing ID. |

|                     |                      | 0xCD             | R              | 1    | -                                                                                                                                         |

| 0x3                 | Device ID            | 0x01             | R              | 0    | Device ID and revision.<br>0x01 for Altra.                                                                                                |

|                     |                      | 0x02             | R              | 0    | Device ID and revision.<br>0x02 for Altra Max.                                                                                            |

|                     |                      | 0xA0             | R              | 1    | 0xA0 for revision A0.<br>0xA1 for revision A1.                                                                                            |

|                     |                      |                  |                |      | OxB0 for revision B0.<br>OxB1 for revision B1 and so on.                                                                                  |

### 5.3 Capability Register Definitions

The Capability Registers provide various capability information about the underlying hardware and firmware. *Table 4* describes these registers in detail.

#### Table 4: Capability Register Definitions

| REGISTER<br>ADDRESS | REGISTER<br>NAME                  | INITIAL<br>VALUE | ACCESS<br>TYPE | BYTE | REGISTER DESCRIPTION                                                                                                                                   |

|---------------------|-----------------------------------|------------------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x5                 | Analog<br>Sensor<br>Support       | _                | R              | 0    | Analog Sensor Support:<br>0: Reserved.<br>1: SoC VR Temp.<br>2: DIMM VR Temp.<br>3: Core VR Temp.<br>4: DIMM Temp.<br>5: RCA VR Temp.<br>67: Reserved. |

|                     |                                   | _                | R              | 1    | 07: Reserved.                                                                                                                                          |

| 0x6                 | Analog Power<br>Sensor<br>Support | _                | R              | 0    | 0: DIMM VR1 Power.<br>1: DIMM VR2 Power.<br>2: Core VR_Power.<br>3: SoC_VR_Power.<br>4: RCA VR Power<br>57: Reserved.                                  |

|                     |                                   | _                | R              | 1    | Reserved.                                                                                                                                              |

| REGISTER<br>ADDRESS | REGISTER<br>NAME                       | INITIAL<br>VALUE | ACCESS<br>TYPE | BYTE | REGISTER DESCRIPTION                                                                                                                                                               |

|---------------------|----------------------------------------|------------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x7                 | Analog<br>Voltage<br>Sensor<br>Support | _                | R              | 0    | 0: DIMM VR1 Voltage.<br>1: DIMM VR2 Voltage.<br>2: Core VR Voltage.<br>3: SoC VR Voltage.<br>4: RCA VR Voltage.<br>57: Reserved.                                                   |

|                     | Analog<br>Current<br>Sensor<br>Support | _                | R              | 1    | 0: DIMM VR1 Current.<br>1: DIMM VR2 Current.<br>2: Core VR Current.<br>3: SoC VR Current.<br>4: RCA VR Current.<br>57: Reserved.                                                   |

| 0x8                 | Other<br>Capabilities                  | _                | R              | 0    | <ul> <li>0: Reserved.</li> <li>1: ACPI Collaborative Processor Performance Control (CPPC) support.</li> <li>2. ACPI Power limit control support.</li> <li>37: Reserved.</li> </ul> |

|                     |                                        | _                | R              | 1    | Reserved.                                                                                                                                                                          |

| OxB                 | Core Cluster<br>Count                  | -                | R              | 0    | The number of dual-core clusters in the processor; Altra has<br>up to 40 core clusters and Altra Max has up to 64.<br><b>Note:</b> The offset is non-sequential.                   |

|                     |                                        | _                | R              | 1    | Reserved                                                                                                                                                                           |

| 0xC                 | System<br>Cache/                       | _                | R              | 0    | Number of PCIe controllers.<br>This is the number of PCIe controllers in the platform.                                                                                             |

|                     | PCle Count                             | _                | R              | 1    | Number of System Level Caches (SLCs).<br>The number of SLCs instantiated in the platform.                                                                                          |

| 0xD                 | Socket Info                            | 0x1              | R              | 0    | 0: Socket0 presence.<br>1: Socket1 presence.                                                                                                                                       |

|                     |                                        | 0x0              | R              | 1    | Reserved.                                                                                                                                                                          |

| OxE                 | Socket TDP                             | _                | R              | 01   | Socket TDP in watts.                                                                                                                                                               |

| 0xF                 | Socket TM1                             | -                | R              | 01   | Socket TM1/T <sub>CI</sub> in °C.                                                                                                                                                  |

### 5.4 Logical Power Sensor Definitions

Processor firmware provides a framework for accessing sensors, using a functional model in which board-specific firmware reports logical power sensor data.

The sensor data format follows:

• OxFFFF – This sensor data is either missing or is not supported by the device.

Check the listed associated Analog Sensor Support registers to determine whether a sensor is supported (analog sensor support bit is set to 1). If the sensor is supported, 0xFFFF value of the corresponding sensor register indicates whether the value is valid (0) or invalid (1).

A sensor is invalid if:

- It is not supported as indicated by the Analog Sensor Support register bit.

- It is not present (such as a missing DIMM) or if the sensor is not supported by the (replaceable) device (such as lack of support by the DIMM type for temperature reading). Reading this sensor returns the value 0xFFFF.

Table 5 summarizes logical sensor definitions.

| Table 5: Logical Power Sensor Register Definition | Table 5: Lo | gical Power | Sensor R | Register | Definitions |

|---------------------------------------------------|-------------|-------------|----------|----------|-------------|

|---------------------------------------------------|-------------|-------------|----------|----------|-------------|

| REGISTER<br>ADDRESS | REGISTER<br>NAME   | INITIAL<br>VALUE | ACCESS<br>TYPE | BYTE | REGISTER DESCRIPTION                                                                                                                                                                                  |

|---------------------|--------------------|------------------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x10                | SoC<br>Temperature | -                | R              | 0    | 9-bit temperature in °C, ranging from -255 to +256.<br>Byte0: LSB of the temperature.<br>Bit 0-7: Temperature.                                                                                        |

|                     |                    | _                | R              | 1    | Byte1: MSB of the temperature.<br>Bit 0: Temperature.<br>Bit 1-7: Reserved.                                                                                                                           |

| 0x11                | SoC VRD<br>Temp    | _                | R              | 01   | Highest temperature reported by the SoC VRDs:<br>Same format as SoC Temperature.<br><b>Note</b> : SoC VRD corresponds to the +0V8_VDDC_SOC_S0 of<br>the Mt Jade reference design.                     |

| 0x12                | DIMM VRD<br>Temp   | _                | R              | 01   | Highest temperature reported by both DIMM VRDs:<br>Same format as SoC Temperature.<br><b>Note</b> : DIMM VRDs correspond to the +1V2_VDDQ0123_S0<br>and +2V2_VDDQ4567_S0 of Mt Jade reference design. |

| 0x13                | Core VRD<br>Temp   | _                | R              | 01   | Highest temperature reported by the Core VRDs:<br>Same format as SoC Temperature.<br><b>Note</b> : Core VRD corresponds to the +0V75_PCP_S0 of Mt<br>Jade reference design.                           |

| 0x14                | CH0 DIMM0<br>Temp  | _                | R              | 01   | Temperature of DIMM0 on CH0:<br>Same format as SoC Temperature.                                                                                                                                       |

| 0x15                | CH1 DIMM0<br>Temp  | _                | R              | 01   | Temperature of DIMM0 on CH1:<br>Same format as SoC Temperature.                                                                                                                                       |

| 0x16                | CH2 DIMM0<br>Temp  | -                | R              | 01   | Temperature of DIMM0 on CH2:<br>Same format as SoC Temperature.                                                                                                                                       |

| 0x17                | CH3 DIMM0<br>Temp  | -                | R              | 01   | Temperature of DIMM0 on CH3:<br>Same format as SoC Temperature.                                                                                                                                       |

| 0x18                | CH4 DIMM0<br>Temp  | -                | R              | 01   | Temperature of DIMM0 on CH4:<br>Same format as SoC Temperature.                                                                                                                                       |

| 0x19                | CH5 DIMM0<br>Temp  | -                | R              | 01   | Temperature of DIMM0 on CH5:<br>Same format as SoC Temperature.                                                                                                                                       |

| 0x1A                | CH6 DIMM0<br>Temp  | _                | R              | 01   | Temperature of DIMM0 on CH6:<br>Same format as SoC Temperature.                                                                                                                                       |

| Ox1B                | CH7 DIMM0<br>Temp  | _                | R              | 01   | Temperature of DIMM0 on CH7:<br>Same format as SoC Temperature.                                                                                                                                       |

| REGISTER<br>ADDRESS | REGISTER<br>NAME      | INITIAL<br>VALUE | ACCESS<br>TYPE | BYTE | REGISTER DESCRIPTION                                                                                                                                                                                        |

|---------------------|-----------------------|------------------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x1C                | RCA VRD<br>Temp.      | -                | R              | 01   | Highest temperature reported by the RCA VRD.<br>Same format as SoC temperature.                                                                                                                             |

| Ox1D —<br>Ox1F      | -                     | —                | —              | _    | Reserved.                                                                                                                                                                                                   |

| 0x20                | Core VRD<br>Power     | _                | R              | 01   | The average power in 5 seconds<br>10-bit power consumption in watts range from 0 to 1023.<br>Byte 0: (LSB).<br>07: Power Consumption.<br>Byte 1: (MSB).<br>01: Power Consumption.<br>27: Reserved.          |

| 0x21                | SoC IO Power          | _                | R              | 01   | This is the SoC IO power which includes the SoC, PCIe, DDR,<br>PHY powers (Non-Core power)<br>Same format as Core VRD Power.                                                                                |

| 0x22                | DIMM VRD1<br>Power    | -                | R              | 01   | Same format as Core VRD Power.                                                                                                                                                                              |

| 0x23                | DIMM VRD2<br>Power    | _                | R              | 01   | Same format as Core VRD Power.<br>Power as reported by the second DIMM VRD (if available).                                                                                                                  |

| 0x24 –<br>0x25      | _                     | _                | _              | -    | Reserved.                                                                                                                                                                                                   |

| 0x26                | Core VRD<br>Power mW  | _                | R              | 01   | The average power in 5 seconds<br>Same format as Core VRD Power. This is the mW portion<br>(remainder) of Core VRD Power.<br>The total Core VRD Power is calculated as sum of<br>registers 0x20 and 0x26.   |

| 0x27                | SoC IO<br>Power mW    | _                | R              | 01   | Same format as Core VRD Power. This is the mW portion<br>(remainder) of SoC IO Power.<br>The total SoC VRD Power is calculated as the sum of<br>registers 0x21 and 0x27.                                    |

| 0x28                | DIMM VRD1<br>Power mW | _                | R              | 01   | Same format as Core VRD Power. This is the mW portion<br>(remainder) of DIMM VRD1 Power.<br>The total DIMM VRD1 Power is calculated as the sum of<br>registers 0x22 and 0x28.                               |

| 0x29                | DIMM VRD2<br>Power mW | _                | R              | 01   | Same format as Core VRD Power. This is the mW portion<br>(remainder) of DIMM VRD2 Power.<br>The total DIMM VRD2 Power is calculated as the sum of 0x23<br>and 0x29.                                         |

| 0x2A                | RCA VRD<br>Power      | _                | R              | 01   | <ul><li>10-bit power consumption in watts range from 0 to 1023.</li><li>Byte 0: (LSB).</li><li>07: Power Consumption.</li><li>Byte 1: (MSB).</li><li>01: Power Consumption.</li><li>27: Reserved.</li></ul> |

| REGISTER<br>ADDRESS | REGISTER<br>NAME        | INITIAL<br>VALUE | ACCESS<br>TYPE | BYTE | REGISTER DESCRIPTION                                                                                                                                          |

|---------------------|-------------------------|------------------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x2B                | Reserved                | _                | R              | 01   | Reserved.                                                                                                                                                     |

| 0x2C –<br>0x31      | _                       | _                | —              | _    | Reserved.                                                                                                                                                     |

| 0x32                | MEM HOT<br>Threshold    | _                | R/W            | 01   | Same format as SoC Temperature.<br>MEM HOT Threshold is the value at which a DIMM triggers<br>its MEMHOT event when its temperature exceeds the<br>threshold. |

| 0x33                | SoC VR HOT<br>Threshold | _                | R/W            | 01   | Same format as SoC Temperature.                                                                                                                               |

| 0x34                | Core VRD<br>Voltage     | _                | R              | 01   | Core voltage:<br>15-bit voltage in mV.                                                                                                                        |

| 0x35                | SoC VRD<br>Voltage      | _                | R              | 01   | SoC voltage:<br>15-bit voltage in mV.                                                                                                                         |

| 0x36                | DIMM VRD1<br>Voltage    | _                | R              | 01   | DIMM VRD1 voltage:<br>15-bit voltage in mV.                                                                                                                   |

| 0x37                | DIMM VRD2<br>Voltage    | _                | R              | 01   | DIMM VRD2 voltage:<br>15-bit voltage in mV.                                                                                                                   |

| 0x38                | RCA VRD<br>Voltage      | _                | R/W            | 01   | RCA VRD voltage:<br>15-bit voltage in mV.                                                                                                                     |

| 0x39                | Core VRD<br>Current     | -                | R              | 01   | Core Current:<br>15-bit current in mA.                                                                                                                        |

| 0x3A                | SoC VRD<br>Current      | _                | R              | 01   | SoC Current:<br>15-bit current in mA.                                                                                                                         |

| 0x3B                | DIMM VRD1<br>Current    | _                | R              | 01   | DIMM VRD1 current:<br>15-bit current in mA.                                                                                                                   |

| 0x3C                | DIMM VRD2<br>Current    | _                | R              | 01   | DIMM VRD2 current:<br>15-bit current in mA.                                                                                                                   |

| 0x3D                | RCA VRD<br>Current      | _                | R              | 01   | RCA VRD current:<br>15-bit current in mA.                                                                                                                     |

| 0x3E –<br>0x3F      | _                       | _                | _              | _    | Reserved.                                                                                                                                                     |

| 0x40                | CH0 DIMM1<br>Temp       | -                | R              | 01   | Temperature of DIMM1 on CH0:<br>Same format as SoC Temperature.                                                                                               |

| 0x41                | CH1 DIMM1<br>Temp       | _                | R              | 01   | Temperature of DIMM1 on CH1:<br>Same format as SoC Temperature.                                                                                               |

| 0x42                | CH2 DIMM1<br>Temp       | _                | R              | 01   | Temperature of DIMM1 on CH2:<br>Same format as SoC Temperature.                                                                                               |

| 0x43                | CH3 DIMM1<br>Temp       | _                | R              | 01   | Temperature of DIMM1 on CH3:<br>Same format as SoC Temperature.                                                                                               |

| REGISTER<br>ADDRESS | REGISTER<br>NAME  | INITIAL<br>VALUE | ACCESS<br>TYPE | BYTE | REGISTER DESCRIPTION                                            |

|---------------------|-------------------|------------------|----------------|------|-----------------------------------------------------------------|

| 0x44                | CH4 DIMM1<br>Temp | -                | R              | 01   | Temperature of DIMM1 on CH4:<br>Same format as SoC Temperature. |

| 0x45                | CH5 DIMM1<br>Temp | _                | R              | 01   | Temperature of DIMM1 on CH5:<br>Same format as SoC Temperature. |

| 0x46                | CH6 DIMM1<br>Temp | _                | R              | 01   | Temperature of DIMM1 on CH6:<br>Same format as SoC Temperature. |

| 0x47                | CH7 DIMM1<br>Temp | _                | R              | 01   | Temperature of DIMM1 on CH7:<br>Same format as SoC Temperature. |

| 0x48 –<br>0x4F      | _                 | -                | -              | -    | Reserved.                                                       |

### 5.5 GPI Mask Register Definitions

These registers are used to control (enable or disable) different alert sources. Each bit indicates whether a status is enabled or disabled.

These registers are initialized to defaults at boot time and can be updated by BMC. The BMC can set a bit in this register to one to enable, or to zero to disable the reporting of such an alert. If an alert source is not supported, the corresponding bit is shown as disabled, and any attempt to enable it has no effect.

- 1: Disabled the alert of the corresponding source

- 0: Enabled the alert of corresponding source

Table 6 describes the GPI Mask registers in detail.

**Note:** A value (0xFFFF) is returned when reading any GPI registers (mask/status/source registers) is invalid value. BMC should consider ignoring this transaction and restart it.

#### Table 6: GPI Mask Register Definitions

| REGISTER ADDRESS | REGISTER NAME  | INITIAL VALUE | ACCESS TYPE | BYTE | REGISTER DESCRIPTION                                                                                         |

|------------------|----------------|---------------|-------------|------|--------------------------------------------------------------------------------------------------------------|

| 0x50             | GPI Control #0 | 0x80          | R/W         | 0    | <ul><li>02: Reserved.</li><li>3: Platform Booting.</li><li>4: Critical Stop.</li><li>57: Reserved.</li></ul> |

|                  |                | -             | _           | 1    | Reserved                                                                                                     |

| 0x51             | GPI Control #1 | 0x07          | R/W         | 0    | 0: SoC VR HOT/Warn/Fault.<br>1: Core VR HOT/Warn/Fault.<br>2: DIMM VRD HOT/Warn/Fault.<br>37: Reserved.      |

|                  |                | -             | —           | 1    | Reserved.                                                                                                    |

| 0x52             | GPI Control #2 | 0x01          | R/W         | 0    | 0: DIMM HOT.<br>1: NVDIMM-N Event.<br>2: Refresh Rate Event.<br>37: Reserved                                 |

|                  |                | _             | _           | 1    | Reserved.                                                                                                    |

| REGISTER ADDRESS | REGISTER NAME  | INITIAL VALUE | ACCESS TYPE | BYTE | REGISTER DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|----------------|---------------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x53             | GPI Control #3 | OxEF          | R/W         | 0    | 0: Core Errors.<br>1: Memory Errors.<br>2: Reserved.<br>3: PCIe Errors.<br>4: Reserved.<br>5: Other SoC Errors.<br>6: ACPI state change.<br>7: Boot Errors.                                                                                                                                                                                                                            |

|                  |                | 0x01          | R/W         | 1    | 0: RAS internal error.<br>17: Reserved.                                                                                                                                                                                                                                                                                                                                                |

| 0x54             | GPI CE/UE Mask | 0x45          | R/W         | 0    | <ul> <li>GPI Uncorrectable Error (UE)/CE<br/>mask:</li> <li>O: Core CE.</li> <li>1: Core UE.</li> <li>2: DIMM CE.</li> <li>3: DIMM UE.</li> <li>4: Reserved.</li> <li>5: Reserved.</li> <li>6: PCIe CE.</li> <li>7: PCIe UE.</li> <li>A 1 bit indicates a mask of an error<br/>type. Masking an error prevents GPI<br/>for the alert and updating the status<br/>registers.</li> </ul> |

|                  |                | 0x01          | R/W         | 1    | 0: Other.<br>17: Reserved.<br>A 1 bit indicates a mask of an error<br>type.                                                                                                                                                                                                                                                                                                            |

| 0x55 – 0x5F      | _              | _             | _           | _    | Reserved.                                                                                                                                                                                                                                                                                                                                                                              |

### 5.6 GPI Source Registers

Each bit in the GPI Source registers, summarized in *Table 7*, denotes the presence or absence of a specific alert source. A value of 1 indicates that an ALERT is present. If an alert source is not supported, it appears as 0. If any alert source is present, the SMBALERT signal is triggered to the BMC to notify the alert. When the BMC clears all alert sources, the processor deactivates the SMBALERT signal and continues to update alert sources.

Upon receiving an SMBALERT signal from the processor, the BMC must first read the GPI Data Set register to determine which GPI Data Set (Data Set #0/Data Set #1/Data Set #2/Data Set #3) register is read next to determine the source of the alert(s). For GPI Data Set #0, each bit already indicates the associated status of the Alert source. For GPI Data Set #1/#2/#3, the BMC must read the corresponding GPI Status registers to find more details about the alerts.

### Table 7: GPI Source Register Definitions

| REGISTER<br>ADDRESS | REGISTER<br>NAME | INITIAL<br>VALUE | ACCESS<br>TYPE | BYTE | REGISTER DESCRIPTION                                                                                                                                                                                                                                                                                            |

|---------------------|------------------|------------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x60                | GPI Data Set     | 0x0              | R              | 0    | <ul> <li>Each bit in this register denotes the presence of one or more alerts in the Global Alert data sets:</li> <li>0: Data set #0.</li> <li>1: Data set #1.</li> <li>2: Data set #2.</li> <li>3: Data set #3.</li> </ul>                                                                                     |

|                     |                  |                  |                | 1    | Reserved.                                                                                                                                                                                                                                                                                                       |

| 0x61                | GPI Data Set #0  | 0x0              | R              | 0    | <ul> <li>02: Reserved.</li> <li>3: Platform Booting.</li> <li>4: Critical Stop.</li> <li>57: Reserved.</li> <li>For platform booting, see Boot stage registers.</li> <li>A failure that triggers the system to stop normal functionality triggers Critical Stop. An example is TPC over temperature.</li> </ul> |

|                     |                  |                  |                | 1    | Reserved.                                                                                                                                                                                                                                                                                                       |

| 0x62                | GPI Data Set #1  | 0x0              | R              | 0    | <ul> <li>0: SoC VR HOT/Warn/Fault.</li> <li>1: Core VR HOT/Warn/Fault.</li> <li>2: DIMM VR HOT/Warn/Fault.</li> <li>37: Reserved.</li> <li>Note: Read the VRD, Core, and DIMM VRD registers to identify which VRD controller is HOT/Warn/Fault.</li> </ul>                                                      |

|                     |                  |                  |                | 1    | Reserved.                                                                                                                                                                                                                                                                                                       |

| 0x63                | GPI Data Set #2  | 0x0              | R              | 0    | <ul> <li>0: DIMM HOT (1*).</li> <li>1: NVDIMM-N Event (2*).</li> <li>2: Refresh Rate Event (3*).</li> <li>37: Reserved.</li> <li>Note <ul> <li>(1*): Read the DIMM Hot Error to identify which DIMM channel is HOT.</li> </ul> </li> </ul>                                                                      |

|                     |                  |                  |                |      | (2*): Read the NVDIMM-N Event Information register<br>(0xB8) to identify the event.                                                                                                                                                                                                                             |

|                     |                  |                  |                |      | (3*): Read the Memory Channel Refresh Rate Status<br>(0x96) to identify which channel is in 2X refresh rate.                                                                                                                                                                                                    |

|                     |                  |                  |                | 1    | Reserved.                                                                                                                                                                                                                                                                                                       |

| REGISTER<br>ADDRESS | REGISTER<br>NAME | INITIAL<br>VALUE | ACCESS<br>TYPE | BYTE | REGISTER DESCRIPTION                                                                                                                                                                   |

|---------------------|------------------|------------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x64                | GPI Data Set #3  | 0x0              | R              | 0    | 0: Core Errors.<br>1: Memory Errors.<br>2: Reserved.<br>3: PCIe Errors.<br>4: PCIe Hot Plug.<br>5: Other Errors.<br>6: ACPI State Change.<br>7: Boot Errors.<br>0: RAS internal error. |

|                     |                  |                  |                |      | 1-7: Reserved.                                                                                                                                                                         |

| 0x65 – 0x6F         | -                | -                | -              | 01   | Reserved                                                                                                                                                                               |

Table 8 provides additional information about the behavior of interrupts and lists the alerts that the BMC can clear.

| Table 8: GPI Interrupt Alert Behaviors Definition | Table 8: 0 | iPI Interrup | t Alert Beha | viors Definitions |

|---------------------------------------------------|------------|--------------|--------------|-------------------|

|---------------------------------------------------|------------|--------------|--------------|-------------------|

| GPI STATUS             | MEANING                                              | GPI BEHAVIOR                                                                           |

|------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------|

| Platform Booting       | The processor is booting.                            | Triggered by CPU or SoC when it starts booting.                                        |

| Critical Stop          | CPU halts.                                           | Triggered by CPU when OS crashes or certain events cause the CPU to hang.              |

| SoC VR Hot             | VR for SoC is in<br>HIGHTEMP.                        | Triggered by CPU when VR for SoC is in HIGHTEMP.                                       |

| Core VR Hot            | VR for CPM is in<br>HIGHTEMP.                        | Triggered by CPU when VR for Core is in HIGHTEMP.                                      |

| DIMM VRD Hot           | VRD for DIMM is in HIGHTEMP.                         | Triggered by CPU when VRD1 for DIMM is in HIGHTEMP.                                    |

| DIMM Hot               | DIMM[y] at channel<br>[x] is in HIGHTEMP.            | Triggered by CPU when any DIMM at any channel is in HIGHTEMP.                          |

| Core Errors            | CPM/CPU has some errors.                             | Triggered by CPU when Core has an error.                                               |

| Memory Errors          | Memory has some errors.                              | Triggered by CPU when Memory has an error.                                             |

| System Cache<br>Errors | System cache has some errors.                        | Triggered by CPU when system cache has an error.                                       |

| PCle Errors            | PCIe has some errors.                                | Triggered by CPU when any PCIe controller has any error.                               |

| PCIe Hot Plug          | PCIe hot plug has<br>some actions<br>(remove/insert) | Triggered by a PCIe hot plug when devices are removed from or inserted into PCIe ports |

| Other Errors           | All other errors.                                    | Triggered by CPU when run-time watchdog expires.                                       |

| GPI STATUS                  | MEANING                                 | GPI BEHAVIOR                                                                                                                                              |

|-----------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| In-band firmware<br>upgrade | In-band firmware<br>upgrade is executed | Triggered by CPU when any firmware component is upgraded via in-band process. BMC must read registers to determine which firmware component is upgraded.  |

| ACPI State Change           | ACPI state change.                      | Triggered by CPU when it has any change of ACPI S-State. BMC should read register System State to determine the target state that the system has entered. |

| Boot Errors                 | System cannot boot properly.            | Triggered by CPU when system cannot boot properly. BMC should read registers to determine how many times boot failed and boot status.                     |

### 5.7 GPI Status Registers

The GPI Source registers provide the alert source, while the GPI Status registers specify the alert that occurs on that source. *Table 9* summarizes the details of each register. When the BMC receives an alert notification, the BMC must read the corresponding GPI Status registers to determine more about the alert. Depending upon the alert, the BMC must handle and clear the alert.

#### Table 9: GPI Status Register Definitions

| REGISTER<br>ADDRESS | REGISTER NAME                                 | INITIAL<br>VALUE | ACCESS<br>TYPE | BYTE | REGISTER DESCRIPTION                                                                                                                                                                                                                                                                              |

|---------------------|-----------------------------------------------|------------------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x70                | Core, DIMM, SLC,<br>PCIe, and Other<br>errors | 0x0              | R              | 0    | Bit mask: Identifies availability of Core, DIMM, SLC,<br>PCIe, and Other errors:<br>Bit 0: Core CE error.<br>Bit 1: Core UE error.<br>Bit 2: DIMM CE error.<br>Bit 3: DIMM UE error.<br>Bit 4: Reserved.<br>Bit 5: Reserved.<br>Bit 5: Reserved.<br>Bit 6: PCIe CE error.<br>Bit 7: PCIe UE error |

|                     |                                               | 0x0              | R              | 1    | Bit 0: Other CE error.<br>Bit 1: Other UE error.<br>Bit 27: Reserved.                                                                                                                                                                                                                             |

| 0x71 -<br>0x77      | Reserved                                      | 0x0              | R/W            | 01   | Reserved.                                                                                                                                                                                                                                                                                         |

| REGISTER<br>ADDRESS | REGISTER NAME              | INITIAL<br>VALUE | ACCESS<br>TYPE | BYTE | REGISTER DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|----------------------------|------------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x78                | VRD Fault/Warning<br>Error | 0x0              | R/W1C          | 0    | VRD fault/warning event:<br>Bit 0: SoC VRD fault/warning.<br>Bit 1: Core VRD1 fault/warning.<br>Bit 2: Core VRD2 fault/warning.<br>Bit 3: Core VRD3 fault/warning.<br>Bit 4: DIMM VRD1 fault/warning.<br>Bit 5: DIMM VRD2 fault/warning.<br>Bit 6: DIMM VRD3 fault/warning.<br>Bit 7: DIMM VRD3 fault/warning.<br>A fault indicates a fault as reported by the VRD. A<br>warning indicates a warning event as reported by the<br>VRD. For more information, see the VRD specification<br>for fault and warning events. Note that a fault results in<br>VRD shutdown. |

|                     |                            | 0x0              | R/W1C          | 1    | Bit 0: DIMM VRD1 fault/warning.<br>Bit 1: DIMM VRD2 fault/warning.<br>Bit 2: DIMM VRD3 fault/warning.<br>Bit 3: DIMM VRD4 fault/warning.                                                                                                                                                                                                                                                                                                                                                                                                                             |